Available online at http://UCTjournals.com

UCT Journal of Research in Science, Engineering and Technology

UCT. J. Resea. Scien. Engineer. Techno. (UJRSET) 01-09 (2015)

# Evaluation and Comparison of CMOS logic circuits with CNTFET

Mahsa Sedaghat<sup>1</sup>\*, Mahdi Salimi<sup>2</sup>

<sup>1</sup>:Young Researchers and Elite Club, Ardabil Branch, Islamic Azad University, Ardabil, Iran, mahsa.sdt1992@gmail.com. <sup>2</sup>: Department of Engineering, Ardabil Branch, Islamic Azad University, Ardabil, Iran. \*Author for Correspondence

# ABSTRACT

Original Article:

In this paper, a comparison between CMOS and MOSFET base circuits HSPICE is done with software.  $0.13\mu$  CMOS transistor model for simulation and CNTFET Model of Stanford University used. In simulations amounts of power, circuit delay and PDP is calculated and these values were compared at the end. And tried to CNTFET applications of transistors in circuit design, including memory and logic circuits Ternary be expressed.

Received 18 Sep. 2015 Accepted 24 Dec. 2015 Published 30 Dec. 2015

*Keywords:* CMOS, CNTFET, Nanotube

DRAIN

#### Introduction

CNTFET transistors due to their small size and properties of polarity change is expected to be the best alternative for CMOS transistors [1]. Monopolar and bipolar transistors are made in the two samples (Ambipolar) [2]. Ambipolar type because of the variability of the electrical signal polarity, is suitable for the implementation of programmable logic circuits. But now CNTFET transistors are unstable [3]. After making the transistor to give a good answer in some cases, but sometimes, it's not good properties and does not answer well. Even with pessimistic assumptions CNTFET nano electronics can be achieved remarkable performance compared to silicon technology. Electronic conductivity and thermal conductivity of nanotubes good or even better than precious metals. The mechanical strength of carbon nanotubes is very high. The benefits of a good system of CNT-based electronic devices is expected, However, many of the challenges of technology and materials for them. Controlled growth of CNT still needs to dominate. In connection to the source/drain on CNT ideal mechanism for better estimating the performance of the device is required. Replacing the metal connection joint CNT Source/Body with a very high doped source/drain (ohmic like) can improve the device performance.

# 2. CNTFET

In 1991, for first time Sumio Iijima observed carbon nanotubes [4]. A carbon nanotube in CNTFET is placed between drain and source of the transistor, Fig.1. This model is based on Stanford CNTFET model [5].

GATE

#### Figure 1: CNTFET transistor

SOURCE

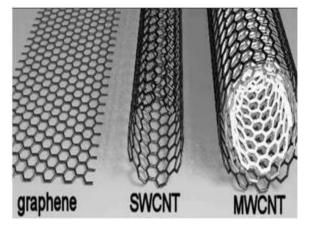

CNTFET have some Features, like: low cost and high degree of reliability. When gate lengths are scaled down in nanoscales, it results in various crucial challenges and reliability issues that may reduce its potential for energy efficient applications [6]. Typical electrical properties of CNTFETs like higher speed, higher dielectric constant and stability provides good characteristics than Silicon based MOSFETs [7]. There are different classifications for CNTFET structures, like: 1. Multi Wall CNT (MWCNT): Each CNT contains several hollow cylinders of carbon atoms nested inside each other, 2. Single Wall CNT (SWCNT): that is made of just a single layer of carbon atoms. These are most common type of CNTFET. Fig.2 represents different types of CNTFET.

CNTs have a diameter of a few nanometers and it's between 0.7nm to 0.3nm in single walled CNT [8]. The diameter of the CNT is directly related to the carbon-carbon distance  $(a_0)$  and the chiral vectors (n,m) [9].

$$D_{CNT} = \frac{\sqrt{3}a_0}{\pi}\sqrt{n^2 + m^2 + nm}$$

(1)

In Ao Teng thesis [13], The physical properties of CNTs have been provided and summarized in Table 1.

Figure 2: Types of CNTFET transistors

| Symbol         | Name                            | Formula                                                                                                        | Value                                                                                     |

|----------------|---------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| a              | Lattice constant                | $a = \sqrt{3}a_{ee} \simeq 2.46\text{\AA}$                                                                     | $a_{cc} = 1.42$ Å                                                                         |

| $a_{1}, a_{2}$ | Basic vectors                   | $\left(\frac{\sqrt{3}}{2};\frac{1}{2}\right)a, \left(\frac{\sqrt{3}}{2};-\frac{1}{2}\right)a$                  | -                                                                                         |

| $b_1, b_2$     | Reciprocal-lattice vectors      | $\left(\frac{1}{\sqrt{3}};1\right)\frac{2\pi}{a},\left(\frac{1}{\sqrt{3}};-1\right)\frac{2\pi}{a}$             |                                                                                           |

| Ch             | Chiral vector                   | $C_h = na_1 + ma_2 \equiv (n,m)$                                                                               | $(0 \le  m ) \le n$                                                                       |

| $d_t$          | Tube diameter                   | $d_t = \frac{ C_h }{\pi} = \frac{a}{\pi}\sqrt{n^2 + nm + m^2}$                                                 | ÷                                                                                         |

| θ              | Chiral angle                    | $\sin \theta = \frac{\sqrt{3}m}{2\sqrt{n^2 + nm + m^2}}$ $\cos \theta = \frac{2n + m}{2\sqrt{n^2 + nm + m^2}}$ | $ \left( 0 \le  \theta  \le \frac{n}{6} \right) \\ \tan \theta = \frac{\sqrt{3}m}{2n+m} $ |

| T              | Translational vector            | $T = t_1 a_1 + t_2 a_2 \equiv (t_1, t_2)$<br>$t_1 = \frac{2m + n}{N_R}, t_2 = -\frac{2n + m}{N_R}$             | $gcd(t_1, t_2) = 1^a$<br>$N_R = gcd (2n + m, 2m + n)^a$                                   |

| Nc             | Number of C atoms per unit cell | $N_c = \frac{4(n^2 + nm + m^2)}{N_e}$                                                                          | 5                                                                                         |

\*gcd(n,m) denotes the greatest common divisor of the two integers n and m.

# 3. Simulation of CMOS Circuits

#### 3.1. Inverter simulation with CMOS

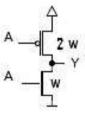

To make the simulation results can be compared with CNTFET model should achieve results in the best mode transistor. In other words, the size of transistors in Hspice determined in such a way that the lowest power consumption and minimal delay achieved (to determine the optimal W). To do this, we have V=0.13 $\mu$  and W between values  $w_{max}$  and  $w_{min}$  the transistor model file is marked as  $0.13\mu$  and  $100\mu$  our Swipe. But here we have Swipe  $6\mu$  as for larger values for W, output from the ideal state is removed. The p-type transistor channel width should be 2 times the n-type (Fig.3).

Figure 3: CMOS inverter circuit and transistor size network display pg and pd.

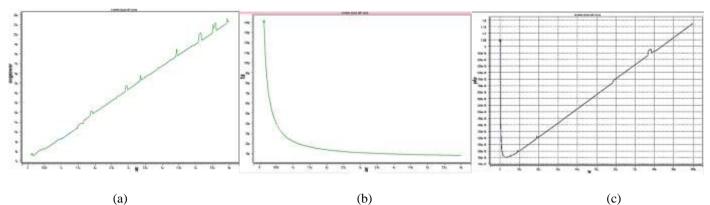

The charts can be, in terms of delay and PDP draw w. Graphs throughput, delay and PDP, respectively, in the form of fig.4 are shown. In each chart, the minimum point for comparison with the circuit CNTFET, obtains.

Figure 4: (a) Chart based on changes in average power consumption w, (b) Chart delay (td) in terms of changes w, (c) PDP graph according to w.

In the diagram Fig. 4(a), the lowest power consumption for w=0.13 $\mu$ , **avg power** min=7.64 $\mu$  obtained. In graph w least delay, delay times  $td_{min}$ =7.8p, respectively (in the fall and rise delays as the delay circuit, whichever is greater). According to the chart PDP w, for w = 2.87 $\mu$ , PDP<sub>min</sub> = 149a, respectively.

For w =  $2.87\mu$  best PDP (lowest PDP) was obtained for the w, delay and average power by 10.7p, and 14  $\mu$ , respectively. The values obtained are summarized in Table 2 were brought.

Table 2: minimum amount of delay and average power inverter circuit PDP

| inverter circuit r Dr.  |                     |                     |

|-------------------------|---------------------|---------------------|

|                         | W                   |                     |

| Td <sub>min</sub>       | 7.8p                | 6 <mark>µ</mark>    |

| Avgpower <sub>min</sub> | 7.64 <mark>µ</mark> | 0.13 <mark>µ</mark> |

| PDP <sub>min</sub>      | 149a                | 2.87 <mark>µ</mark> |

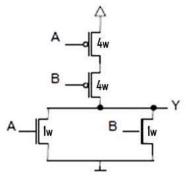

#### 3.2. NOR Simulation with CMOS

In this circuit should be optimized for the inverter obtained from the w (w =  $2.87 \,\mu$  the inverter circuit was at least PDP), use. As in Figure 3has been found to be 4 times the width of the transistors is pu network.

Figure 5: CMOS Circuit of NOR the size of the transistors and display networks pd and pu.

To get the THD should delay obtained on all tracks. Nor is it because the output circuit of 12 passes for 4 to switch the tracks so we need only calculate td related to the 4-pass. According to the truth table, we identified the 4 modes (Table 3) and delay for each individual obtains. Delays are to be calculated separately must zero in Hspice input B and input A applied to the circuit (Fig.6), and to obtain  $td_{rise1}$  and  $td_{fall1}$ . The zero input A and input B are applied to the circuit and to obtain  $td_{rise2}$  and  $td_{fall2}$ .

Figure 6: zero entry B and apply the AC input circuit for calculating tdrise1 and tdfall1.

|  | Table 3: NOR | properly and | passages that are | e changing the output mode. |

|--|--------------|--------------|-------------------|-----------------------------|

|--|--------------|--------------|-------------------|-----------------------------|

۵

| Α | B | Y=NOR(A,B) |

|---|---|------------|

| 0 | 0 | 1          |

| 0 | 1 | 0          |

| 1 | 0 | 0          |

| 1 | 1 | 0          |

(a)

And the maximum amount of delay is considered as the main circuit delay. To calculate the PDP, the average power consumption should be multiplied by average rtd. Average power consumption avg power nor = 29.84u respectively.

Tdnor=tdmax=16.98p

avgpowernor=29.84u  $Avgtd_{nor} = (td_{fall1} + td_{fall2} + td_{rise1} + td_{rise2})/4 = 17.85p$ Pdpnor=Avgtdnor\*Avgpowernor=532.644a

#### **3.3. NAND Simulation with CMOS**

In this circuit, the optimal w obtained for the least PDP the inverter circuit, respectively (w = 2.87u), we use. Shape and width of transistors in the circuit shown below (Fig.7).

| A            | В               | Y               | Name Delay | Delay  |

|--------------|-----------------|-----------------|------------|--------|

| 8            | 0 <b>→</b> 1    | 1>0             | elfall2    | 16.69p |

| 8            | 1 <b>&gt;</b> 0 | 0 <b>→</b> 1    | tirise2    | 13.13p |

| u <b>→</b> 1 | 0               | 1 <b>&gt;</b> 0 | Hist       | 24.6p  |

| 1>0          | 0               | I>I             | thrisel    | 15.56  |

Figure 7: CMOS Circuit of NAND and display the size of transistors networks pd and pu.

In Table (4), 4 through which the output will change with the amount Delays.

| Α | В | Y=NAND(A,B) |

|---|---|-------------|

| 0 | 0 | 1           |

| 0 | 1 | 1           |

| 1 | 0 | 1           |

| 1 | 1 | 0           |

(a)

The circuit delay, be average and PDP are given below.

Td<sub>nand</sub>=td<sub>max</sub>=20.02p Avgpowernand=24.64u  $Avgtd_{nand} = (td_{fall1} + td_{fall2} + td_{rise1} + td_{rise2})/4 = 14.6p$  $Pdp_{nand} = Avgtd_{nand} * Avgpower_{nand} = 359.16a$

#### 4. Simulation of CNTFET Circuits 4.1. Inverter simulation with CNTFET

In CNTFET transistors in order the changing some parameters, the value of power and delay change. Among these parameters, the gate length (Lgate) and the tube (the

number of nanotube in a transistor) are. To obtain the least possible delay, the first Swipe Lgate we (the tube to be desired) and the optimization of the chart Lgate

Table 4: nand truth table and passages that are changing the output mode. B Name Delay ¥ Belay

| 1               | 0 <b>&gt;</b> 1 | 1>0             | effall2  | 13.03p |

|-----------------|-----------------|-----------------|----------|--------|

| 1               | ı <b>→</b> 0    | <b>0</b> →1     | telrise2 | 20.02p |

| a <b>→</b> i    | 1               | 1>0             | Hallt    | 10.47p |

| 1 <b>&gt;</b> 0 | 1               | 0 <b>&gt;</b> 1 | Mrisel   | 14.88p |

| 1               | (1.)            |                 |          |        |

(b)

(b)

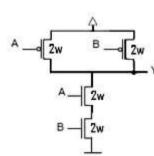

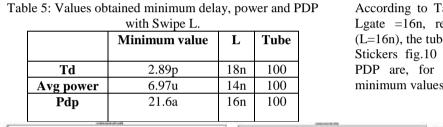

PDP-Lgate (for minimum PDP) obtains. Then for this Lgate optimal value, we switch tube and the PDP-tube graph tube optimized value (for the lowest PDP) also obtains. So in this way the Lgate optimization and optimal tube is obtained. The inverter circuit transistor size network CNTFET pu and pd are the same shape (Fig.8).

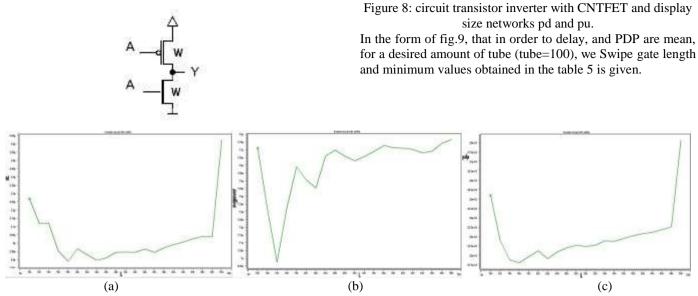

Figure 9: (a) Graph delay in changes L, (b) Average power consumption graph based on changes L, (c) PDP graph changes according to L.

According to Table 4 above Gate optimum value for PDP, Lgate =16n, respectively. However, for the gate length (L=16n), the tube in the area where output is ideal, we Swipe. Stickers fig.10 that respectively delay, average power and PDP are, for Lgate=16n and Swipe obtained tube and minimum values in the table 6 is given.

Figure 9: (a) Delay Chart according to tube change, (b) Average power consumption graph according to tube change, (c) PDP graph according to tube change.

Pdp

| According to the diagram fig. 10(a),(b) With the rise of tube |

|---------------------------------------------------------------|

| delay circuit is low but the power consumption increases.     |

| Table 6: Values obtained minimum delay, power and PDP         |

with Swipe tube.

|           | Minimum value | tube | L   |

|-----------|---------------|------|-----|

| Td        | 2.95p         | 100  | 16n |

| Avg power | 2.24u         | 9    | 16n |

After reaching the lowest PDP shall optimal use Lgate =16n and tube = 80. The circuitry as CMOS circuitry supplement, not static power consumption. And only when switch power is consumed (Fig.11).

21.3a

80

16n

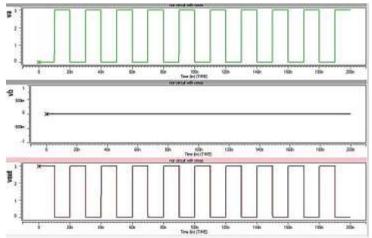

Figure 11: input voltage, output voltage and instantaneous power inverter circuit with CNTFET.

#### 4.2. NOR Simulation with CNTFET

In this circuit Lgate and optimal tube obtained for the least PDP the inverter circuit was CNTFET (Lgate=16N and tube=80), we use. The width of the transistor in the circuit and is shown below.

Figure 12: NOR Circuit with CNTFET and display the size of transistors networks pd and pu.

Table (6) 4 through which change can be output with the amount Delays.

Table 7: NOR truth table and passages that are changing the output mode.

| Α | B | Y=NOR(A,B) |

|---|---|------------|

| 0 | 0 | 1          |

| 0 | 1 | 0          |

| 1 | 0 | 0          |

| 1 | 1 | 0          |

|            |                 | tifali2 | 2.66p |

|------------|-----------------|---------|-------|

| <b>→</b> 0 | <b>□</b> →1     | 4       |       |

|            |                 | tdrise2 | 6.09p |

| 0          | 1>0             | ufall   | 2.36p |

| 0          | 0 <b>&gt;</b> 1 | thrisel | 4.88p |

|            |                 | 0 0     | 0 0   |

(a)

The circuit delay, be average and PDP are given below.  $Td_{nor}=td_{max}=6.09p$   $avgpower_{nor}=5.8u$  $Avgtd_{nor}=(td_{fall1}+td_{fall2}+td_{rise1}+td_{rise2})/4=3.99p$

Pdp<sub>nor</sub>=Avgtd<sub>nor</sub>\*Avgpower<sub>nor</sub>=23.14a **4.3. NAND Simulation with CNTFET**

The circuit also obtained for the least PDP Lgate and optimal tube that was CNTFET inverter circuit (Lgate=16n and tube=80), we use. Shape and width of transistors in the circuit shown below (Fig.13).

Figure 13: NAND Circuit with CNTFET and display the size of transistors networks pd and pu.

#### **Takestan Institute of Higher Education**

#### Table 8, 4 through which change can be output with the amount Delays.

(b)

Table 8: NAND truth table and passages that will change the output mode.

| А | В | Y=NAND(A,B) |

|---|---|-------------|

| 0 | 0 | 1           |

| 0 | 1 | 1           |

| 1 | 0 | 1           |

| 1 | 1 | 0           |

|   | `  |

|---|----|

| ( | a) |

| L | a) |

|   |    |

The circuit delay, be average and PDP are given below.  $Td_{nand}$ =td<sub>max</sub>=6.1p Avgpower<sub>nand</sub>=5.87u

$\begin{array}{l} Avgtd_{nand} = (td_{fall1} + td_{fall2} + td_{rise1} + td_{rise2})/4 = 4.01 p \\ Pdp_{nand} = Avgtd_{nand} * Avgpower_{nand} = 23.54 a \\ \end{array}$

# 5. Compare the results CMOS and CNTFET technology

As the table 9 is determined based on technology circuits CNTFET, compared to the technology CMOS (0.13  $\mu$ ), in

| A           | B   | Y            | Name Delay | Delay |

|-------------|-----|--------------|------------|-------|

| 1           | ∎>I | ı→ı          | stial 2    | 4.7p  |

| 1           | 1>0 | ı <b>→</b> ı | thrise?    | 2.55p |

| <b>I</b> →I | 1   | ı <b>→</b> ı | stall      | 6.1p  |

| 1>0         | 1   | 0>1          | térisel    | 2.69p |

terms of delay, power consumption and PDP have between 70 to 90 percent improvement.

|  | Table 9: | Comparison | of the results | obtained from | simulations |

|--|----------|------------|----------------|---------------|-------------|

|--|----------|------------|----------------|---------------|-------------|

| GATE                 | CMOS Technology |           | CNTFET Technology |       |              |        |

|----------------------|-----------------|-----------|-------------------|-------|--------------|--------|

|                      | Td              | Avg power | pdp               | Td    | Avg power    | pdp    |

| INVERTER             | 7.8p            | 7.64u     | 149a              | 2.89p | 4.24u        | 21.3a  |

| NOR                  | 24.6p           | 29.84u    | 532.6a            | 6.09p | 5.8u         | 23.14a |

| NAND                 | 20.02p          | 24.64u    | 359.16a           | 6.1p  | 5.87u        | 23.54a |

| AVG                  | 17.47p          | 20.69u    | 346.92a           | 5.03p | 5.3u         | 22.66a |

| Improvement vs. Cmos | -               | -         | -                 | 71.2% | 74.3%        | 93.46% |

|                      |                 |           |                   |       | LOGIC SYMBOI | S      |

# 6. Designed inverter logic gate three (ternary) with transistors CNTFET

## 6.1. Summary of ternary logic

Tuesday is valued logic. 0, 1 and 2 respectively for false representation, defined and used correctly [10]. However, some of the undefined references 0, 1 and 2 indicate wrong is correct [11]. Each variable n {x 1, ..., X} of the ternary f (x) as a logical function mapping  $\{0,1,2\}^n$  of  $\{0,1,2\}$  is defined in the x={x1,..., xn}. Ternary logic operations can be defined as low.

$$\begin{split} X_i, X_j \in \{0, 1, 2\} \Longrightarrow \begin{cases} X_i + X_j = \max(X_i, X_j) \\ X_i. X_j = \min(X_i, X_j) \\ \overline{X}_i = 2 - X_i \end{cases} \end{split}$$

(2)

Operators +,. And - to represent the practice of OR, and AND, NOT in their Ternary logic. The basic logic circuits ternary, inverter, Nor and Nand Gates are. Ternary logic symbols showed in the table 10.

#### Table 10: ternary logic symbols

| Voltage Level       | Logic Value |

|---------------------|-------------|

| 0                   | 0           |

| 1/2 V <sub>dd</sub> | 1           |

| V <sub>dd</sub>     | 2           |

Ternary logic gates based on the equations (2) are designed.

#### 6.2. The definition of inversion in logic Ternary (three)

A typical inverter input of a single gate x, and 3 outputs (not defined y0, y1 and y2) are as follows.

$$y_{0} = c_{0}(x) = \begin{cases} 2 & \text{if } x = 0 \\ 0 & \text{if } x \neq 0 \end{cases}$$

$$y_{1} = c_{1}(x) = \overline{x} = 2 - x$$

(3)

$$y_{2} = c_{2}(x) = \begin{cases} 2 & \text{if } x \neq 2 \\ 0 & \text{if } x = 2 \end{cases}$$

So, to implement an inverter ternary, 3 inverter is required. The 3 inverter, inverter negative ternary (NTI), the standard ternary inverter (STI) and inverter positive Ternary (PTI)

requirements. If y0, y1 and y2 output equations (3), the truth table of the table 11 is.

| Table 11: Logic table Inverters STI, PTI and N | ΓI |

|------------------------------------------------|----|

| TRUTH TABLE OF STI, PTI, AND NTI               |    |

| Input X | STI | PTI | NTI |

|---------|-----|-----|-----|

| 0       | 2   | 2   | 2   |

| 1       | 1   | 2   | 0   |

| 2       | 0   | 0   | 0   |

# 6.3. NAND and NOR logic operation defined in ternary (triple)

This ternary logic gates are for multiple entries. Triple NAND and NOR logic input equations, functions as below.

$$Y_{NAND} = \min(X_1, X_2)$$

(4)

$$Y_{NOR} = \overline{Max\{X_1, X_2\}}$$

Ternary logic gates NAND and NOR truth table (Table 12) are displayed.

(5)

| Table 12: the right gate NOR and NAND. |

|----------------------------------------|

| TRUTH TABLE OF NAND AND NOR            |

| Input X <sub>1</sub> | Input X <sub>2</sub> | YNAND | Y <sub>NOR</sub> |

|----------------------|----------------------|-------|------------------|

| 0                    | 0                    | 2     | 2                |

| 1                    | 0                    | 2     | 1                |

| 2                    | 0                    | 2     | 0                |

| 0                    | 1                    | 2     | 1                |

| 1                    | 1                    | 1     | 1                |

| 2                    | 1                    | 1     | 0                |

| 0                    | 2                    | 2     | 0                |

| 1                    | 2                    | 1     | 0                |

| 2                    | 2                    | 0     | 0                |

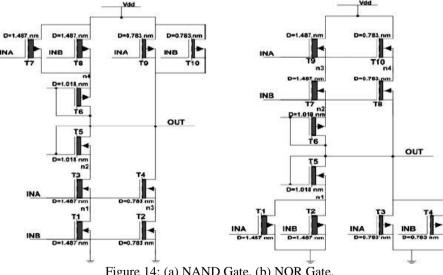

## 6.4. NAND and NOR logic gates designed in three (ternary) with transistors CNTFET

Ternary logic NAND and NOR logic transistor CNTFET in equations 4 and 5 show. The circuits in Fig.14 have been brought.

Figure 14: (a) NAND Gate, (b) NOR Gate.

.

Each transistor gate 10 CNTFET are three different chirality. They are similar to CMOS binary circuits except that the threshold voltages are different. The two gate like STI circuit in Fig. 14, transistors with diameters 1.487nm, nm 0.783 and

1.018nm respectively threshold voltage v 0.289, v 0.559 and v 0.428 respectively

#### **Takestan Institute of Higher Education**

# 7. Conclusions

According to numerous studies that have been done CNTFET and optimization methods to solve their shortcomings to be challenged, despite many benefits that these devices are still a long way to MOSFET in industrial applications CNTFET there, As yet the growth of unwanted metal tubes during manufacture CNTs is an important challenge and a negative impact on delay, power and performance are CNT-based circuits. From this perspective, the theoretical and experimental results show clear vision to us. However, the scope for discussion, exchange of ideas and research takes more and more widespread.

#### References

[1] Hodges, David A, "Analysis and Design of Digital Integrated Circuits", In Deep Submicron Technology.3rd ed.c 2003

[2] M.Haykel Ben Jamaa, "Novel library of logic gates with ambipolar CNTFETs", Opportunities for multi-level logic synthesis. 2009: 622-627

[3] M.Haykel Ben Jamaa, David Atienza, Yusuf Leblebici, Giovanni De Micheli:"*Programmable logic circuits based on ambipolar CNFET*", DAC 2008: 339-340.

[4] Lin,S;Kim,Y; Lombardi," *CNTFET-Based Design of Ternary Logic Gates and Arithmetic Circuits*", Nanotechnology, IEEE Transactions on,Volume PP, Issue 99, 0 Page(s):Digital Object Identifier10.1109/TNANO.2009.2036845.

[5] J.Deng, H.-S.P.Wong 200. "A compact SPICE model for carbonnanotube field-effect transistors including nonidealities and its application—Part II: Full device *model and circuit performance benchmarking*", IEEE Trans. Electron Device, vol. 54, no. 12, pp. 3195–3205, Dec. 2007.

[6] Murotiya,S.L., A.Matta, A.Gupta, "*Performance evalution of CNTFET-based SRAM cell design*", Int. J. Electr. Electr. Eng., 2: 78-83, 2012.

[7] Rajendra, P.S., B.K. Madhavi and K.L. Kishore, "*Design of low write-power consumption SRAM cell based on CNTFET at 32nm Technology*". Int. J. VLSI Design Commun. Syst., 2: 167-177, 2012.

[8] Rasmita Sahoo and R. R. Mishra, "*Simulations of Carbon Nanotube Field Effect Transistors*", International Journal of Electronic Engineering Research, ISSN 0975- 6450, Volume 1 Number 2 (2009) pp.117–125.

[9] Avichal Sahai, Vikas Sharma, "*Design of Low Power CNTFET Based D Flip Flop using Sleep Transistor Technique*", International Journal of Engineering Research & Technology (IJERT), ISSN: 2278-0181, Vol. 4 Issue 04, April-2015.

[10] S.Iijima 1991. "*Helical microtubules of graphitic carbon*", Nature, vol.354, no.6348, Nov. 1991, pp.56-8. (2002).

[11] Jorge Pedraza Arpasi:"A Brief Introduction to Ternary Logic", November 2003.

[12] Stanford University CNFET Model website[Online2008].Available:

http://nano.stanford.edu/model.php id=23.

[13] Ao Teng, "*Physical Properties of Carbon Nanotubes*", Dept of Physics, Uni. of Tennessee, 2010.